Ako se radi 'pasivna konverzija' (koje inace nisam zagovornik), onda se napon pojavljuje na nekom MALOM otporu u protivnom se narusava konstantnost struje izvora u DAC-u (pri tom ne mislim na jedan izvor nego vise njih koji se ukljucuju po potrebi da bi se dobila ukupna izlazna struja. TO sto ce u PARALELU s time biti spojeno pojacalo s visokom ulaznom impedancom ni najmanje ne povecava otpor koji vidi DAC. Spoj dva paralelna otpora uvijek ima manji otpor od bilo kojeg od njih. 1 iz osnova elektrotehnike.

Veliki otpor koji vidi DAC je slabo rešenje, treba ti mali otpor, virtualna nula.

Sklop za naponsko pojačanje ima veliki ulazni Z, jer je stvoren da ne opterečuje izlaz. Ako staviš u paralelu 100R i 100K (dif amp za naponsko pojačanje), onda imaš 99.9R, nije to virtualna nula.

Nadalje, SVAKI strujni izlaz ima odredjenu toleranciju na naponski hod u protivnom cijeli DAC ne bi imao toleranciju u naponima napajanja. Jedno povlaci drugo i to na trivijalan nacin, tako da, nadam se, ne moram to objasnjavati. Ono sto se pojavljuje je izoblicenje, i to tim vece cim je naponski hod veci. Sama po sebi je ta pojava neizbjezna, pitanje je koliko iznosi u odnosu na rezoluciju DAC-a.

To su dodobra obradili Walt Jung i Walt Kester, mislim, da imaš i online na Waltovom sajtu,

http://waltjung.org Toleranciju na napon napajanja vidiš sa slike. Za 5V napajanje situacija je još gora, a kamoli za 3.3V. Vodi računa da ti je PSRR DAC čipa mali, u momentu tranzicije max 6 dB.

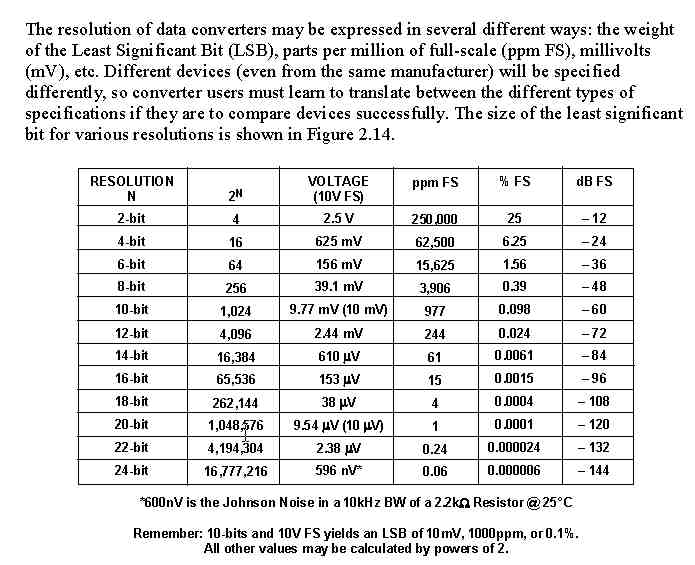

- LSB_err.jpg (49.17 KiB) Pogledano 8432 put/a.

Iz ovog si vec pokupio 1 iz osnova. Strujni ula podrazumijeva neku vrstu virtualne nule, sto je jednako lako ili tesko ostvariti bilo SE ili diferencijalno.

Strujni ulaz je virtualna nula, ali samo "virtualna", ne mora biti na 0V, može biti na +2V DC, ako želiš, ali ostaje virtualna nula.

Promašio si point, želio sam da kažem, da ne radiš konverziju iz diff na SE, nego možeš upotrebiti I/V konverter na diff izlazu Vout DAC čipa.

ASRC, ako veruješ, da anulira jitter, onda veruješ u bajke proizvodjača i Vudu magiju. ASRC ulazni jitter ugradjuje u izlaz, u stvari ga re-distribuira po čitavom pojasu. Nema sideband peaka, ako nekada uradiš spektralnu analizu izlaza, vidječeš.

Neču se više upletati i smetati. Želim samo reći da izbegni ASRC, nemoj raditi diff na SE konverziju, pogotovo sklopom sa naponskim pojačanjem (diff amp) i budi kreativniji od žutih, koji nemaju kreativitet i rade DAC prema datasheetu proizvodjača.

A CS8416 obavezno terati aktivnim ulazom, ali ne sa time:

http://www.audiofil.hr/forum/forum_post ... 556#392556Več se godinu dana smijemo na tu shemu