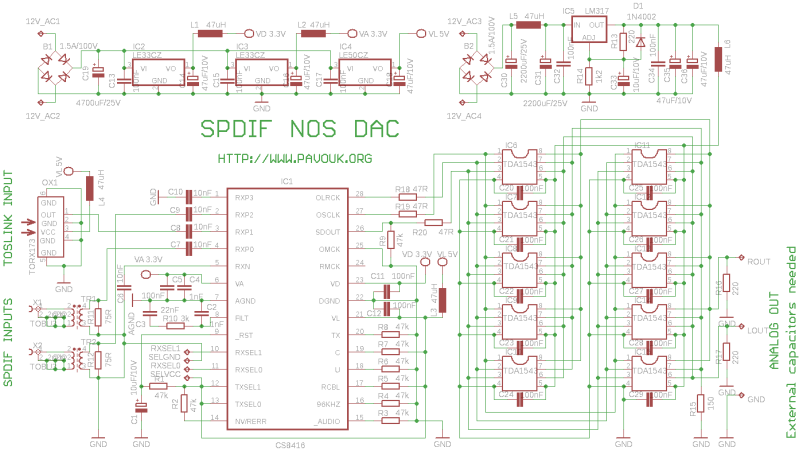

Grunfe, ajmo po redu. Prvo, jesi li sa skopom proviril da li na izlazima iz CSA8416 (pinovi 26, 27 i 28) imas data i clock signale amplitude otprilike napona napajanja (ako je sve ka na shemi sa Vl od 5V tribal bis imat TTL nivoe)

kad je CS8416 odvojen od svih TDA1543 (znaci sam za sebe). Ako to imas, ne tribas se obazirat na sadrzaj signala na ta 3 pina, CS u tom slucaju sigurno radi kako triba.

Ako to imas dok je CS odvojen a spajanjem sa TDA1543 neka od te 3 linije (ili sve) padne na nulu ili se digne na high ili uocis da je doslo do kakve deformacije signala, onda je ili CS preopterecen tolikim brojem paralelnih DAC chipova ili je neki od TDA1543 chipova krepal pa radi monade. Ne bi smilo bit nikakve vidljive razlike izmedju opterecenog i neopterecenog CS-a, eventualno pad amplitude signala za koji mici postotak i nista vise.

Ako je ovo prvo da ga toliko paralelnih TDA1543 preopterecuje onda ces morat ugradit buffer (ne cijevni

) izmedju CS i TDA a ako je u pitanju to da je neki TDA krepal onda ih moras vadit jednog po jednogdok ne napipas koji je krepal. Valjda si stavil podnozja za njih jer ako nisi morat ces rezat linije dok ne napipas krepanoga

A buffer je i inace jako pozeljno stavit izmedju CS-a i tolikog broja paralelno vezanih potrosaca. Ako zbog niceg drugog onda zato da neminovni kapaciteti spojnih veza medju tolikim potrosacima budu njime odvojeni od samog CS-a

Napon koji sad miris na ulaznim pinovima TDA ti ne triba bit nikakav pokazatelj, njih CS triba vuc gori ili doli. Mozes ih provat (kad je CS odvojen) sa pull up / pull down otpornikom od par K povuc gori i doli i odma vidit da li to slusaju